#### CPE/EE 422/522 Advanced Logic Design L15

Electrical and Computer Engineering University of Alabama in Huntsville

#### **Outline**

- VHDL

- What we know (additional topics)

- Attributes

- · Transport and Inertial Delays

- Operator Overloading

- Multivalued Logic and Signal Resolution

- IEEE 1164 Standard Logic

- Generics

- · Generate Statements

- Synthesis of VHDL Code

- Synthesis Examples

- What we don't know

- Files and Text IO

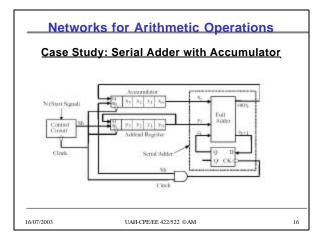

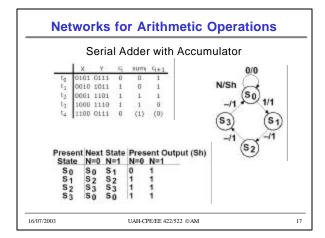

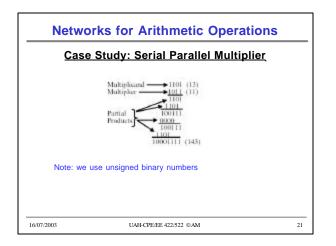

- Networks for Arithmetic Operations

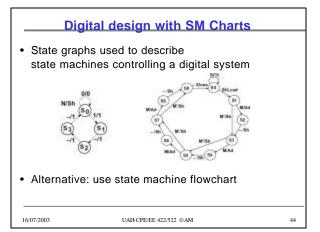

- SM Charts

16/07/2003

JAH-CPE/EE 422/522 @ AM

#### Files

- File input/output in VHDL

- · Used in test benches

- Source of test data

- Storage for test results

- VHDL provides a standard TEXTIO package

- read/write lines of text

16/07/2003 UAH-CPE/EE 422/522 ©AM

#### Files

#### File Declaration

file file-name: file-type [open mode] is "file-pathname";

#### Example:

file test\_data: text open read\_mode is "c:\best1\best.dat"

declares a file named test\_state of type test which is opened in the read mode. The

physical location of the file is in the test1 directory on the c: drive.

#### Modes for Opening a File

read\_mode file elements can be read using a read procedure

write\_made new empty file is created; elements can be written using a write procedure

append\_mode allows writing to an existing file

#### **Standard TEXTIO Package**

- Contains declarations and procedures for working with files composed of lines of text

- · Defines a file type named text:

```

type text is file of string;

```

Contains procedures for reading lines of text from a file of type text and for writing lines of text to a file

16/07/2003

HALL CREEKE 422/522 @ AN

#### **Reading TEXTIO file**

- Readline reads a line of text and places it in a buffer with an associated pointer

- Pointer to the buffer must be of type line, which is declared in the textio package as:

type line is access string;

- When a variable of type line is declared, it creates a pointer to a string

- Code

```

variable buff: line;

...

readline (test_data, buff);

```

reads a line of text from test\_data and places it in a buffer which is pointed to by buff

16/07/2003

UAH-CPE/EE 422/522 © AM

#### Extracting Data from the Line Buffer

- To extract data from the line buffer, call a read procedure one or more times

- For example, if bv4 is a bit\_vector of length four, the call

```

read(buff, bv4)

```

extracts a 4-bit vector from the buffer, sets bv4 equal to this vector, and adjusts the pointer buff to point to the next character in the buffer. Another call to read will then extract the next data object from the line buffer.

16/07/2003

UAH-CPE/EE 422/522 © AM

#### Extracting Data from the Line Buffer (cont'd)

- TEXTIO provides overloaded read procedures to read data of types bit, bit\_vector, boolean, character, integer, real, string, and time from buffer

- Read forms

```

read(pointer, value)

read(pointer, value, good)

```

- good is boolean that returns TRUE if the read is successful and FALSE if it is not

- type and size of value determines which of the read procedures is called

- character, strings, and bit\_vectors within files of type text are not delimited by quotes

16/07/2003

#### Writing to TEXTIO files

Call one or more write procedures to write data to a line buffer and then call writeline to write the line to a file

```

variable buffw : line;

variable int1 : integer;

variable bv8 : bit_vector(7 downto 0);

...

write(buffw, int1, right, 6); --right just., 6 ch. wide

write(buffw, bv8, right, 10);

writeln(buffw, output_file);

```

· Write parameters: 1) buffer pointer of type line,

2) a value of any acceptable type,

3) justification (left or right), and 4) field width (number of characters)

16/07/2003 UAH-CPE/EE 422/522 ©AM

#### An Example

- Procedure to read data from a file and store the data in a memory array

- · Format of the data in the file

- address N comments

byte1 byte2 ... byteN comments

- address 4 hex digits

- N indicates the number of bytes of code

- · bytei 2 hex digits

- · each byte is separated by one space

- · the last byte must be followed by a space

- anything following the last state will not be read and will be treated as a comment

/07/2003 UAH-CPE/EE 422/522 ©AM

10

#### An Example (cont'd)

- · Code sequence: an example

- 12AC 7 (7 hex bytes follow)

AE 03 B6 91 C7 00 0C (LDX imm, LDA dir, STA ext)

005B 2 (2 bytes follow)

01 FC

- TEXTIO does not include read procedure for hex numbers

- we will read each hex value as a string of characters and then convert the string to an integer

- How to implement conversion?

- table lookup constant named lookup is an array of integers indexed by characters in the range '0' to 'F'

- this range includes the 23 ASCII characters:

'0', '1', ... '9', ':', ';', '<', '=', '>', '?', '@', 'A', ... 'F'

• corresponding values: 0, 1, ... 9, -1, -1, -1, -1, -1, -1, 10, 11, 12, 13, 14, 15

16/07/2003 UAH-CPE/EE 422/522 ©AM 11

#

#

#### **Things to Remember**

- · Attributes associated to signals

- allow checking for setup, hold times, and other timing specifications

- Attributes associated to arrays

- allow us to write procedures that do not depend on the manner in which arrays are indexed

- Inertial and transport delays

- allow modeling of different delay types that occur in real systems

- · Operator overloading

- allow us to extend the definition of VHDL operators so that they can be used with different types of operands

16/07/2003 UAH-CPE/EE 422/522 ©AM 14

#### Things to Remember (cont'd)

- Multivalued logic and the associated resolution functions

- allow us to model tri-state buses, and systems where a signal is driven by more than one source

- Generics

- allow us to specify parameter values for a component when the component is instantiated

- Generate statements

- efficient way to describe systems with iterative structure

- TEXTIO

- convenient way for file input/output

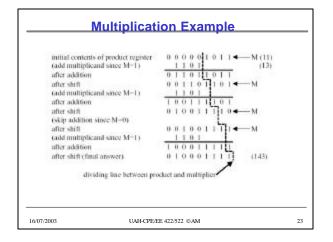

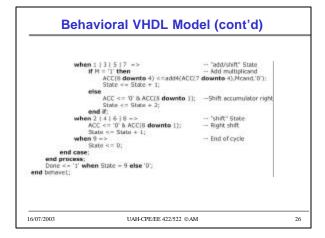

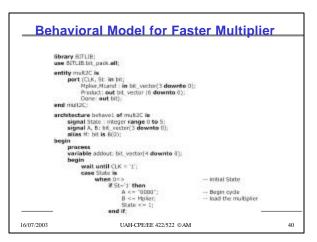

#### **Behavioral VHDL Model** library BITLIB; use BITLIB.bit\_peck.all; entity mult4X4 is port (Clk, St: in bit; Moller, Mcand : in bit\_vector(3 downto 0); Done: out bit); end mult4X4; architecture behavel, of mult4X4 is signal State: integer range 0 to 9; signal ACC: bit\_vector(8 downto 0); alias M: bit is ACC(0); - accumulator - Mis bit 0 of ACC wait until Clk = '1'; case State is -- executes on rising edge of clock -- initial State if St-'1' then ACC(8 downto 4) <= "00000"; — Begin cycle ACC(3 downto 0) <= Npiler; — load the multiplier State <= 1; end if; 16/07/2003 UAH-CPE/EE 422/522 @AM 25

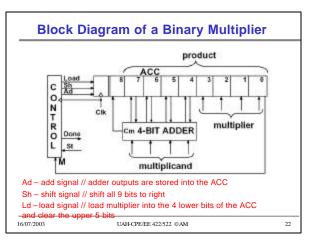

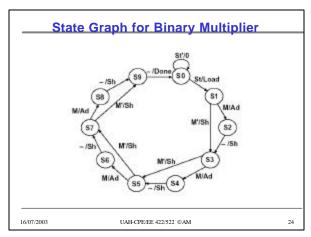

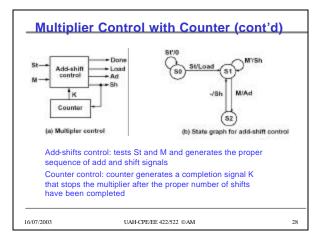

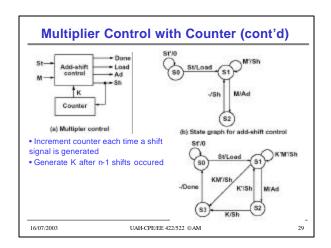

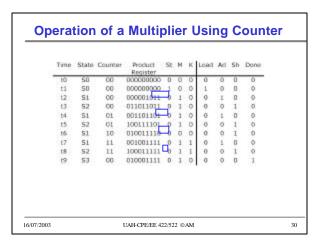

## Multiplier Control with Counter

- Current design: control part generates the control signals (shift/add) and counts the number of steps

- If the number of bits is large (e.g., 64), the control network can be divided into a counter and a shift/add control

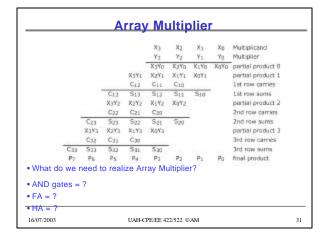

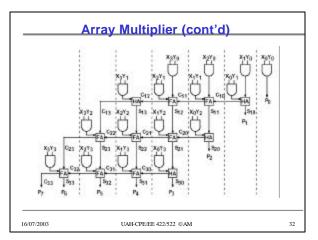

#### **Array Multiplier (cont'd)**

- · Complexity of the N-bit array multiplier

- number of AND gates = ?

- number of HA = ?

- number of FA = ?

- Delay

- tg longest AND gate delay

- tad longest possible delay through an adder

16/07/2003

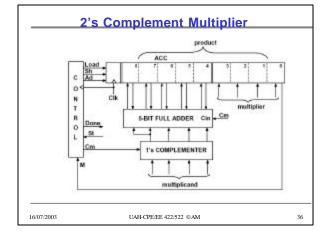

#### **Multiplication of Signed Binary Numbers**

- · How to multiply signed binary numbers?

- Procedure

- Complement the multiplier if negative

- Complement the multiplicand if negative

- Multiply two positive binary numbers

- Complement the product if it should be negative

- · Simple but requires more hardware and time than other available methods

16/07/2003

### **Multiplication of Signed Binary Numbers**

- · Four cases

- Multiplicand is positive, multiplier is positive

- Multiplicand is negative, multiplier is positive

- Multiplicand is positive, multiplier is negative

- Multiplier is negative, multiplicand is negative

- Examples

- $-0111 \times 0101 = ?$

- $-1101 \times 0101 = ?$

- $-0101 \times 1101 = ?$

- 1011 x 1101 = ?

- Preserve the sign of the partial product at each step

- If multiplier is negative, complement the multiplicand before adding it in at the last step

35

#

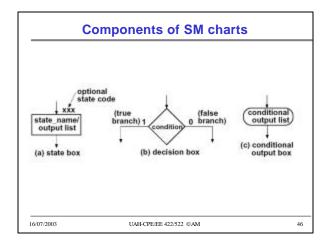

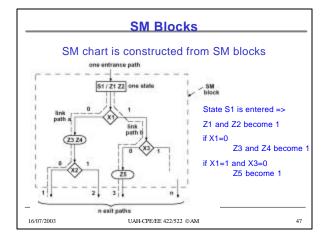

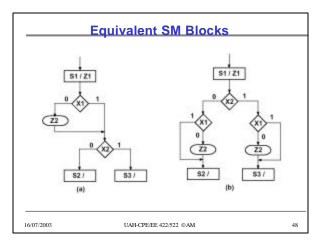

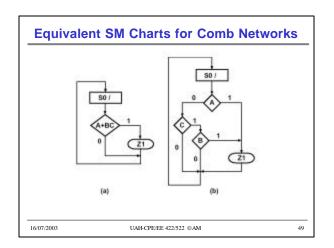

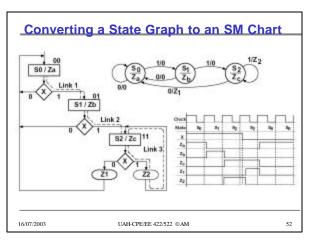

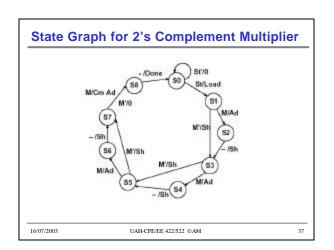

#### **State Machine Charts**

- SM chart or ASM (Algorithmic State Machine) chart

- Easier to understand the operation of digital system by examining of the SM chart instead of equivalent state graph

- SM chart leads directly to hardware realization